HPCおよびAI向けハードウェア 2025-2035年:技術、市場、予測Hardware for HPC and AI 2025-2035: Technologies, Markets, Forecasts 本レポートでは、ハイパフォーマンスコンピューティング(HPC)とAIのハードウェア市場を調査している。El Capitanのような主要なスーパーコンピュータの分析を含め、エクサスケール時代のHPC市場全体の概要を... もっと見る

※ 調査会社の事情により、予告なしに価格が変更になる場合がございます。

サマリー

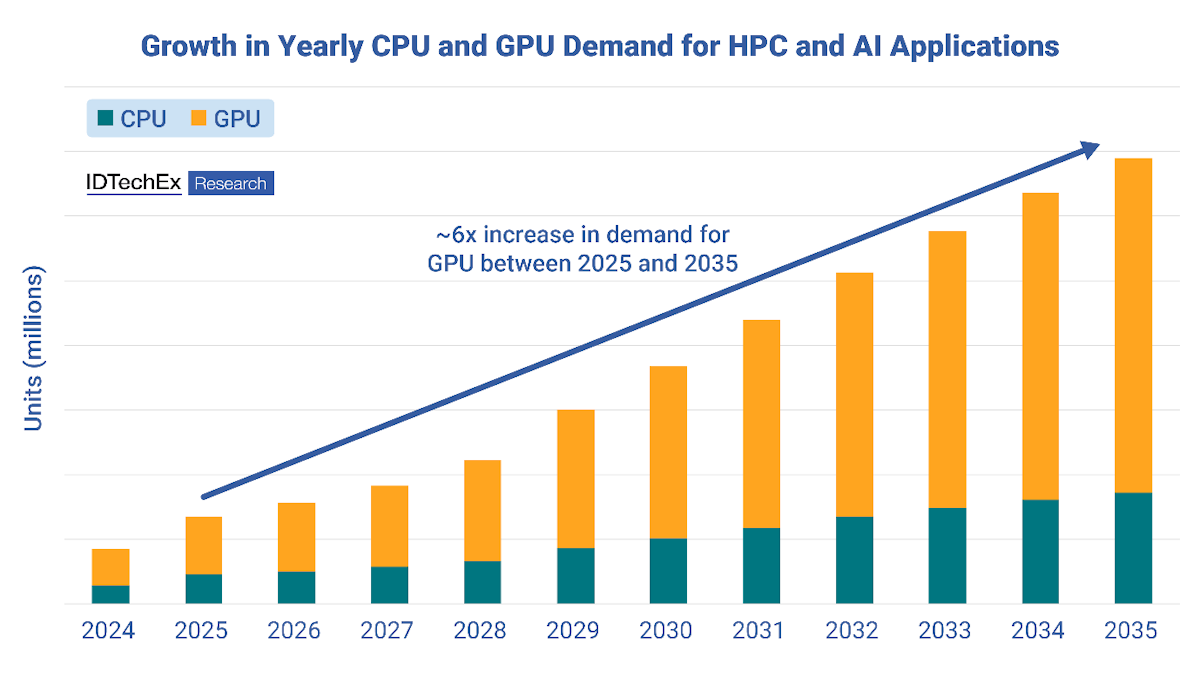

本レポートでは、ハイパフォーマンスコンピューティング(HPC)とAIのハードウェア市場を調査している。El Capitanのような主要なスーパーコンピュータの分析を含め、エクサスケール時代のHPC市場全体の概要を提供しています。GPUやアクセラレータ、CPU、メモリ、先端半導体パッケージング、相互接続、熱管理などの技術に関する詳細な概要を提供するとともに、50人以上のHPC業界プレイヤーのプロフィールを掲載しています。HPCおよびAIハードウェア市場全体と6つの主要ハードウェアクラスについて、2025年から2035年までの数量と収益のきめ細かな予測により、2035年までの市場規模が5,810億米ドルになると予測される、この市場の発展機会の全体像を示しています。

スーパーコンピュータを含むHPCシステムは、多数のプロセッサで処理を並列化することにより、計算速度の点で他のすべてのクラスのコンピューティングを凌駕している。HPCは、エンジニアリング・モデリングの促進から天候予測に至るまで、重要な産業において長年不可欠なツールとなっている。AIや機械学習のユースケースが、その基礎となるモデルの規模とともに成長するにつれ、HPCシステムに対する需要は、その処理能力やコンピューティング・ノード間の相互接続に対する要求とともに、強まる一方です。

1秒間に1,000億回以上の浮動小数点演算を実行できる世界最大のHPCシステムは、世界的な超大国の政府系国立研究所が所有しています。しかし、民間企業も遠く及ばず、Microsoft Azureのようなクラウド・プロバイダーも上位クラスのスーパーコンピューターを所有している。AIの導入が拡大するにつれ、ここでの成長はさらに加速すると予想される。

IDTechExのレポートでは、プロセッサ、メモリ、ストレージ、アドバンストパッケージング、相互接続、熱管理を中心に、HPCにおける主要なハードウェアの課題を検証している。GPUとその他のAIアクセラレータは、GPU内のテンソル処理用コアの採用や、AMDがNVIDIAに挑戦する兆しなど、重要なトレンドを含むプロセッサ分野の見出しを独占している。しかし、CPU市場でも大きな進展があり、AMDのTurinプロセッサのようなチップではコア数が200に近づき、米国のEl Capitanや中国のTianhe-3を含む世界で最も強力なスーパーコンピュータでは、GPUとCPUが同じパッケージに統合された統合ヘテロジニアスシステムが導入されている。

メモリ分野では、HBM(High Bandwidth Memory)の採用がアクセラレータの能力向上に不可欠であり、現在HPCのアクセラレータの約95%がこの技術を採用しているが、セレクタ専用メモリ(SOM)、相変化メモリ(PCRAM)、磁気抵抗RAM(MRAM)などの次世代メモリ技術の研究は、現在のメモリ選択のエネルギー消費量の高さによって推進されている。HPC ワークロードの増大する性能要件を満たす大容量ストレージの追求により、市場で入手可能な一般的な TLC SSD よりも低コストで高密度の QLC SSD が登場しています。

高度なパッケージングは、これらすべてのチップ技術を実現する重要な要素であり、ロジックの上にメモリを3Dスタックすることは、デバイス上の相互接続距離を短縮することで超高帯域幅を実現する最良のアプローチです。NVIDIAのInfiniBandやHPEのSlingshotのような低レイテンシネットワークの将来の反復が、チップスケールでデータが移動しなければならない距離をさらに短縮し、全体的なスループットを高速化するために、コ・パッケージングされた光学系に移行するため、高度なパッケージング技術は、HPCノード間の相互接続のロードマップにとっても非常に重要です。

もちろん、これらの進歩は大量の熱を発生させるため、熱管理性能が鍵となる。運用コストとパフォーマンスにおいて液浸冷却が強力なパフォーマンスを発揮しているにもかかわらず、HPCビルダーがこのような巨大な相互接続マシンの構築に伴う巨額の資本支出を削減しようとしているため、コールドプレート冷却がほとんどのケースで選択されるテクノロジーであり続けることが予想されます。

上記のようなトレンドや、ストレージの発展やこのテクノロジーの成長に影響を与える地政学的ダイナミクスのようなさらなる課題も含め、HPC市場を理解する必要がある人にとって、IDTechExのレポートは必見である。エクサスケール時代の幕開けであり、AI開発にとってこれまでで最も実りの多い時期である今、スーパーコンピューティングの需要は急速な拡大が見込まれている。そのため、『Hardware for HPC and AI 2025-2035』には、HPCハードウェア市場全体だけでなく、CPU、GPU、HBMを含むメモリ、ストレージ、サーバーボードなどの主要ハードウェア技術に関する10年予測が含まれている。読者は、このエキサイティングな業界の現在と未来について、幅広く詳細な情報を得ることができる。

主要な側面

IDTechExの本レポートは、以下の主要な内容をカバーしています:

ハイパフォーマンスコンピューティングアーキテクチャとスーパーコンピュータ:

A) ハイパフォーマンスコンピューティングの主要なアーキテクチャとエクサスケールコンピュータの台頭を含む主要な業界動向の定義。

B) 市場促進要因やトレンド、ケーススタディ、主要OEM、国際貿易の影響、HPCバリューチェーンなど、HPC開発の現状を探る。

HPCとAI用ハードウェアの技術開発

A) ハイパフォーマンス・コンピューティングのためのCPU、GPU、その他のアプリケーション専用ハードウェアなどのプロセッシング・ユニットの現在の開発状況と、これらのシステム内でのAIのニーズの高まりに基づく開発状況を調査する。

B) 高帯域幅メモリ、DDRメモリ、新技術など、ハイパフォーマンス・コンピューティングとAI用のメモリ(RAM)技術の調査。

C) ハイパフォーマンス・コンピューティングにおけるストレージ技術の探求。NANDフラッシュメモリやストレージサーバーでの使用例など、先進的なストレージに焦点を当てる。様々なワークロードに対するストレージ技術の分析を含む。

D) 2.5Dおよび3Dパッケージング技術を使用したチップレット集積への移行など、ハイパフォーマンス・コンピューティング・システムで使用される先端半導体技術の調査。

E) ハイパフォーマンス・コンピューティングにおけるネットワーキングと相互接続のブレークダウン(銅線、プラガブルやコ・パッケージド・オプティクスなどの光ベースのソリューションなど

F) ハイパフォーマンスコンピューティングに使用されるデータセンターシステムの冷却システムの種類と、ハイパワーシステムに対するニーズの高まりに基づく技術動向のレビュー。

G) 全セクションで、比較分析、主要トレンド、ケーススタディ、技術ベンチマーク、主要プレイヤーの動向などを取り上げています。

市場予測と分析:

A) HPCシステムに使用される主要ハードウェア別に、10年間のきめ細かな市場予測。

B) HPCシステムにおける各種ハードウェアの主要技術動向と商業動向の評価。

目次

Summary

この調査レポートでは、ハイパフォーマンスコンピューティング(HPC)とAIのハードウェア市場について詳細に調査・分析しています。

主な掲載内容(目次より抜粋)

Repoert Summary

This report examines the high-performance computing (HPC) and AI hardware markets. It provides an overview of the overall HPC market in the exascale era, including analysis of major supercomputers like El Capitan. Detailed overview of technologies including GPUs and accelerators, CPUs, memory, advanced semiconductor packaging, interconnects, and thermal management is provided, alongside over 50 profiles of HPC industry players, many from primary interviews. Highly granular forecasts from 2025 to 2035 in volume and revenue for the overall HPC and AI hardware market and 6 key classes of hardware provide a picture of the evolving opportunities in this market, with a US$581 billion market value forecast by 2035.

HPC systems, including supercomputers, outclass all other classes of computing in terms of calculation speed by parallelizing processing over many processors. HPC has long been an integral tool across critical industries, from facilitating engineering modelling to predicting the weather. As both the use-cases of AI and machine learning have grown alongside the scale of their underlying models, the demand for HPC systems has only intensified, alongside the demands on their processing power and interconnects between computing nodes.

The largest HPC systems in the world, which can perform over 1 quintillion floating-point operations per second, are the preserve of government-operated national labs of global superpowers. However, private corporations are not far behind, with cloud providers like Microsoft Azure possessing supercomputers in the upper echelons of performance. Growth here is only expected to accelerate as the deployment of AI widens.

IDTechEx's report examines the key hardware challenges in HPC, which revolve around processors, memory and storage, advanced packaging, interconnects, and thermal management. GPUs and other AI accelerators grab all the headlines in the processor space, with important trends including the adoption of cores for tensor processing within GPUs and hints of AMD challenging NVIDIA. However, substantial progress has also taken place in the CPU market, with core counts approaching 200 in chips like AMD's Turin processors and the deployment of integrated heterogeneous systems - GPUs and CPUs integrated into the same package - taking place in the world's most powerful supercomputers, including the USA's El Capitan and China's Tianhe-3.

In the memory space, the adoption of HBM (High Bandwidth Memory) has been crucial to the growing capabilities of accelerators, with approximately 95% of accelerators in HPC now employing the technology, but research into next-generation memory technologies such as selector-only memory (SOM), phase change memory (PCRAM) and magnetoresistive RAM (MRAM) is being driven by the high energy consumption of today's memory choices. The quest for high-capacity storage that meets the increasing performance requirements of HPC workloads is seeing the emergence of high-density QLC SSDs at a lower cost-point than typical TLC SSDs available in the market.

Advanced packaging is a key enabler of all these chip technologies, with the 3D stacking of memory on top of logic being the best approach to achieve ultra-high bandwidths by shrinking on-device interconnect distances. Advanced packaging techniques are also highly important for the roadmaps of the interconnects between HPC nodes, as future iterations of low-latency networks like NVIDIA's InfiniBand and HPE's Slingshot move towards co-packaged optics to further reduce the distances data must travel at the chip scale and speed up throughput overall.

Of course, these advances evolve large amounts of heat, so thermal management performance is key. Despite immersion cooling's strong performance in operational expense and performance, cold plate cooling is expected to remain the technology of choice in most cases as HPC builders seek to reduce the massive capital expenses that come with building these enormous interconnected machines.

For those needing to understand the HPC market, including the above trends and further challenges like the development of storage and the geopolitical dynamics that have affected the growth of this technology, IDTechEx's report is a must. At the dawn of the exascale era and in the most fruitful period for AI development yet, the demand for supercomputing is set for rapid expansion. As such, Hardware for HPC and AI 2025-2035 includes 10-year forecasts not only for the overall HPC hardware market, but for key hardware technologies including CPUs, GPUs, memory including HBM, storage and server boards. The reader will leave equipped with a wide-ranging, in-depth picture of the present and future of this exciting industry.

Key aspects

This report from IDTechEx covers the following key contents:

High-performance computing architectures and supercomputers:

A) Defining key architectures for high-performance computing and key industry trends including the rise of exascale computers.

B) Exploring the current state of HPC development, including market drivers and trends, case studies, major OEMs, the influence of international trade, and the HPC value chain.

Technology developments of hardware for HPC & AI:

A) Exploring current developments of processing units, such as CPUs, GPUs, and other application-specific hardware for high-performance computing and their development based on the increasing need for AI within these systems.

B) Investigating technologies for memory (RAM) for high-performance computing and AI, such as high bandwidth memory, DDR memory, and emerging technologies.

C) Exploring storage technologies in high-performance computing. Focusing on advanced storage, like NAND flash memory and its use cases in storage servers. Includes analysis of storage technologies for various workloads.

D) Investigating advanced semiconductor technologies used in high-performance computing systems, such as the move into chiplet integration using both 2.5D and 3D packaging technologies.

E) Breakdown of networking and interconnects in high-performance computing, such as copper and optical-based solutions like pluggable and co-packaged optics.

F) Review of types of cooling systems in data center systems used for high-performance computing and technology trends based on the growing need for high-power systems.

G) All sections cover comparative analysis, key trends, case studies, technology benchmarks, and developments for key players.

Market forecasts & analysis:

A) 10-year granular market forecasts separated by key hardware used for HPC systems.

B) Assessment of key technological and commercial trends for different hardware in HPC systems.

Table of Contents

ご注文は、お電話またはWEBから承ります。お見積もりの作成もお気軽にご相談ください。本レポートと同分野(半導体)の最新刊レポート

IDTechEx社の 半導体、コンピュータ、AI - Semiconductors, Computing & AI分野 での最新刊レポート

よくあるご質問IDTechEx社はどのような調査会社ですか?IDTechExはセンサ技術や3D印刷、電気自動車などの先端技術・材料市場を対象に広範かつ詳細な調査を行っています。データリソースはIDTechExの調査レポートおよび委託調査(個別調査)を取り扱う日... もっと見る 調査レポートの納品までの日数はどの程度ですか?在庫のあるものは速納となりますが、平均的には 3-4日と見て下さい。

注文の手続きはどのようになっていますか?1)お客様からの御問い合わせをいただきます。

お支払方法の方法はどのようになっていますか?納品と同時にデータリソース社よりお客様へ請求書(必要に応じて納品書も)を発送いたします。

データリソース社はどのような会社ですか?当社は、世界各国の主要調査会社・レポート出版社と提携し、世界各国の市場調査レポートや技術動向レポートなどを日本国内の企業・公官庁及び教育研究機関に提供しております。

|

|

.png)

.png)

.png)