戞11夞丂KGD Packaging & Test Workshop 曬崘拞搰丂榓岹 K-NETS 僐儞僒儖僥傿儞僌幮挿 戞11夞丂KGD Packaging & Test Workshop 曬崘拞搰丂榓岹 K-NETS 僐儞僒儖僥傿儞僌幮挿

2004擭11寧16擔崋

丂僇儕僼僅儖僯傾偺悷傫偩嬻婥偲惵偄嬻偺壓丄KGD(Known Good Die) Packaging and Test Workshop偑崱擭傕儚僀儞偺嶻抧偲偟偰桳柤側僫僷偱9寧12擔偐傜嶰擔娫奐嵜偝傟偨丅戞11夞偲側傞摨Workshop偵偼丄暷崙傪拞怱偵墷廈丄傾僕傾丄擔杮偐傜懡偔嶲壛幰傪廤傔丄10廃擭偲偟偰擌傢偭偨嶐擭傪戝偒偔忋夞傞栺160柤傪悢偊偨丅崱夞偼摿偵暷崙撪偐傜偺嶲壛偑7妱偲崅偔丄WLP傗SiP摍僟僀僾儘僟僋僩傪巊梡偟偨幚憰媄弍傊偺暷崙偺娭怱偺搙崌偄偑塎偊傞丅

奐嵜儂僥儖 (Embassy Suites Swan Napa, California, USA)

拞掚偵偁傞悈幵彫壆傪埻傓抮偲敀捁偨偪

丂崱擭偼丄3偮偺僠儏乕僩儕傾儖偲5偮偺僙僢僔儑儞偑峴側傢傟丄弶傔偰WLP傗SiP傪僥乕儅偲偟偨僙僢僔儑儞偑撈棫偟偰愝偗傜傟偨丅撪梕堦棗偲奺僙僢僔儑儞偺曬崘審悢傪昞侾偵帵偡丅側偍丄暪愝偟偰峀偘傜傟偨揥帵僽乕僗偵偼丄敿摫懱丄幚憰丄僥僗僩娭楢丄晹嵽椶偐傜憰抲娭楢婇嬈傑偱彫婯柾側偑傜24幮偑弌揥偟偨丅

丂摨Workshop傪枅擭庡嵜丄塣塩偟偰偄傞DPC (Die Products Consortium)偼丄暷ISMT (International SEMATECH) 幮摍偵傛傞僾儘僕僃僋僩偺堦偮偲偟偰10擭埲忋慜傛傝慻怐偝傟偨抍懱偱丄暷Texas Instruments丄暷IBM丄暷Agilent Technologies傗暷National Semiconductor摍傪拞怱偵敪懌偟偨丅偦偺屻丄撈Infineon Technologies丄娯崙Samsung Electronics丄暷Intel傗僔儞僈億乕儖STATS (ST Assembly Test Services丄尰STATS ChipPAC)幮摍偑壛傢偭偰尰嵼偼憤悢15幮偑夛堳偲側傝丄崙嵺揑側僟僀僾儘僟僋僩偺巗応傗娐嫬傪惍旛丄惢昳偺昳幙夵慞傗怣棅惈岦忋丄庢埖偄傗幚憰偵娭楢偡傞婯奿採埬側偳丄嬈奅敪揥傪栚巜偟妶摦偟偰偄傞丅

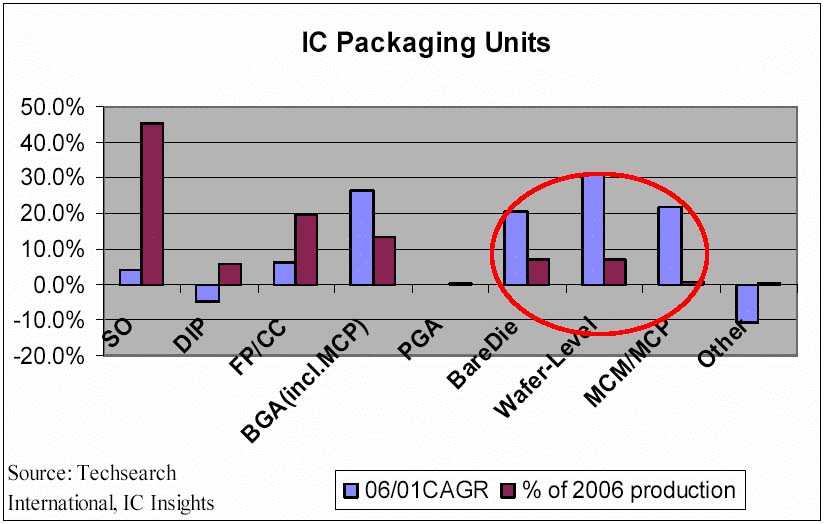

丂DPC偵傛傞僟僀僾儘僟僋僩偺掕媊偼乽敿摫懱僨僶僀僗偺偆偪丄儀傾僠僢僾丄僼儕僢僾僠僢僾偍傛傃僂僄僴儗儀儖 (僠僢僾僗働乕儖) 僷僢働乕僕偲偟偰巗応偵偱偰偄傞惢昳乿偱偁傞丅摨抍懱偺Larry Gilg巵偼丄乽嵟嬤偺媄弍妚怴偵傛傝WLP惢昳偑壛傢偭偨偙偲偱僟僀僾儘僟僋僩巗応偲娭楢婇嬈椞堟偑奼偑偭偰偒偨乿偲弎傋偨丅

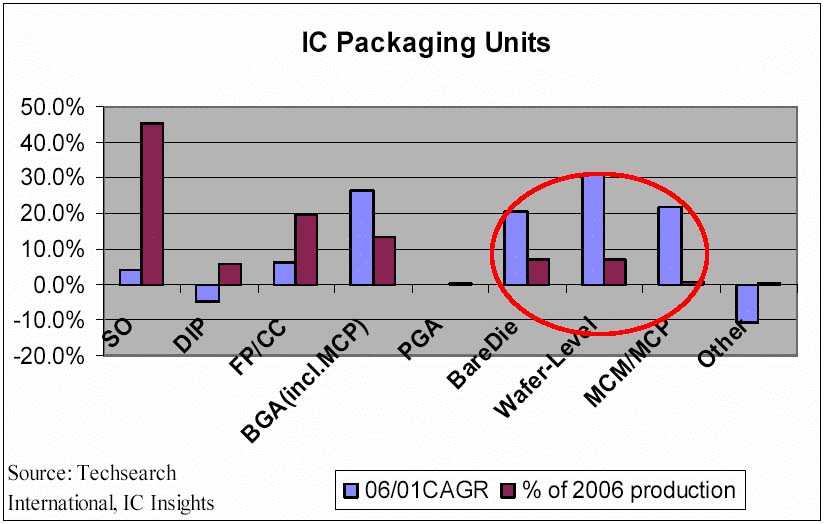

丂暷IC insights幮偲暷Techsearch International幮偵傛傞挷嵏偱偼丄敿摫懱僨僶僀僗巗応偵偍偗傞偙傟傜偺惢昳孮偺惉挿棪偼崅偔丄2001乣2006擭偺5擭娫偺CAGR偑20乣30%偲側傝丄2006擭偵偼擭娫儐僯僢僩悢慡懱偺栺15%傪愯傔傞偲梊應偟偰偄傞丅偙傟偼儅儖僠僠僢僾SiP側偳傪娷傫偩BGA僷僢働乕僕椶偺儐僯僢僩愯桳棪丄惉挿棪偲尐傪暲傋傞悢帤偱偁傞丅暷Techsearch International幮挿偺Jan Vardaman彈巎偼乽儀傾僟僀僾儘僟僋僩偺惉挿偼丄拲栚偝傟傞WLP摍偺怢傃偼傕偪傠傫丄3D僷僢働乕僕丄偡側傢偪僗僞僢僋僷僢働乕僕偺惉挿偑戝偒側栶妱傪扴偭偰偄傞乿偲尵偆丅敿摫懱僠僢僾偺僗僞僢僋幚憰媄弍偼楌巎揑偵尒傟偽15乣20擭偲丄寛偟偰怴偟偄媄弍偱偼側偄偐傕偟傟側偄丅偟偐偟側偑傜丄摉帪傛傝摿庩偱僴僀僄儞僪側椞堟偺傒棙梡偝傟偰偒偨摨媄弍傪柉惗岦偗偵鴫蕮I側Z弍偲偟偰奐壴偝偣偨偺偼丄擔杮婇嬈偺搘椡偵懠側傜側偄偲摨巵偼懕偗偨丅

丂堦曽丄僗僀僗STMicroelectronics幮偺New Package Development VP偱偁傞Carlro Cognetti攷巑偼僗僞僢僋僷僢働乕僕傪SiP偺堦宍懺偲懆偊乽愯桳柺愊偐傜偡傟偽僗僞僢僋傪偼偠傔偲偡傞SiP偼儉乕傾偺朄懃傪挻偊偨廤愊搙傪幚尰壜擻偲偡傞媄弍偱偁傞丅偟偐偟側偑傜丄愝寁僣乕儖傗僔儈儏儗乕僔儑儞僣乕儖摍偺揰偱傑偩傑偩枹弉偱偁傞乿偲丄偦偺栤戣揰傪採婲偟偰偄傞丅

丂KGD媄弍偵栚傪岦偗傞偲丄DRAM偵懳偡傞媍榑偑儂僢僩偲側偭偰偄傞傛偆偩丅暷Micron Technology偺Sr. Fellow偲偟偰摨幮偺僥僗僩媄弍傪棪偄傞Lee Nevill巵偼乽嫊峔偲恀幚乿偲戣偟偰DRAM偵懳偡傞KGD惢昳壔偺崲擄偝傪夝愢偟偨丅

- 嫊峔: KGD偼僷僢働乕僕儞僌僐僗僩偑妡傜側偄暘丄埨壙偱偁傞丅

恀幚:僂僄僴忋偺DRAM僥僗僩偼僷僢働乕僕屻傛傝傕岠棪偑埆偔僐僗僩崅偲側傞丅

- 嫊峔: DRAM偼SRAM傗ASIC摍僨僕僞儖僨僶僀僗摨條偵僥僗僩壜擻偱偁傞丅

恀幚:DRAM偼峔憿忋傾僫儘僌僨僶僀僗摨條偵壛岺屻偺摿惈曄壔傪峫椂偟偨僥僗僩偑昁梫偩丅椺偊偽僂僄僴敄岤壔壛岺偱偼丄岤偝100 mm傪愗傞偲VRT (Variable Retention Time)偺塭嬁偑尰傟傞丅

- 嫊峔: DRAM KGD偼僷僢働乕僕惢昳偲摨儗儀儖偺昳幙偲怣棅惈偑昁梫偩丅

恀幚:偦偺幚尰偵偼僐僗僩偑偍傛偦3攞丄偝傜偵僷僢働乕僕屻偺僥僗僩僐僗僩偑偄偢傟偵偣傛昁梫丅柉惗昳岦偗偵偼梫媮偱偒側偄偩傠偆丅

- 嫊峔: DRAM偵懳偡傞WBIT (Wafer Burn-丂In Test)媄弍偼條乆側岺晇偱姰惉偟偨丅

恀幚:妋偐偵悢偁傞曬崘偑側偝傟偰偼偄傞偑丄偄偢傟傕丄彜梡儀乕僗偵忔傞検嶻岦偗偱偼側偄

丂摿偵(2)偵偮偄偰偼堦斣偺壽戣偱偁傞偲Workshop夛応偺懡偔偺巀摨傪庴偗偰偄偨丅Nevill巵偼乽儕儁傾岺掱偼尰忬DRAM偵偼昁恵偱偁傞丅偙傟偵傛傝丄僟僀僔儞僌壛岺屻偺摨幮DRAM僠僢僾偱栺90%偺廂棪傪堐帩偟偰偄傞乿偲岅偭偨丅

丂偦偺懠丄DRAM偵娭偟偰偼丄僗僞僢僋僷僢働乕僕儞僌屻偺僥僗僩傪晄梫偲偡傞庤朄偺暷Inapac Technologies幮丄慖戰揑Burn-In傗掅僐僗僩Burn-In偺奐敪傪尞偲偡傞暷Secrest Research幮傗暷Aehr Test System幮丄PiP (Package-in-Package)偵傛傞僗僞僢僋媄弍偱栤戣夝寛偡傞偲偄偆暷STATS ChipPAC幮丄偦偟偰儊儌儕岦偗WFP (Wafer-level Fabricated Package)傪奐敪偟偨娯崙Samsung Electronics幮摍傛傝曬崘偑峴側傢傟偨丅

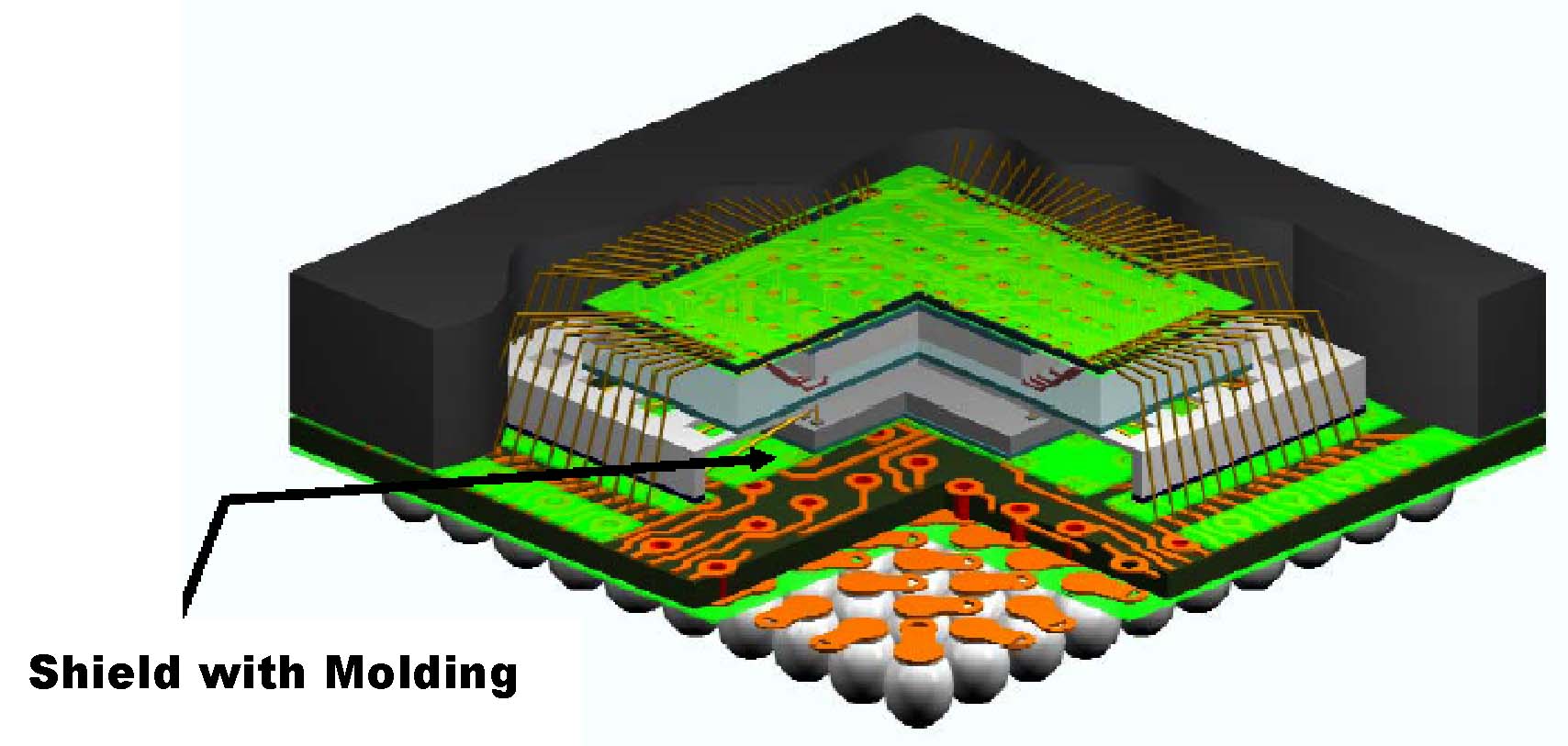

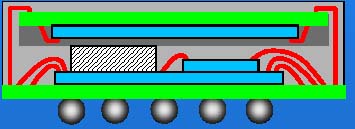

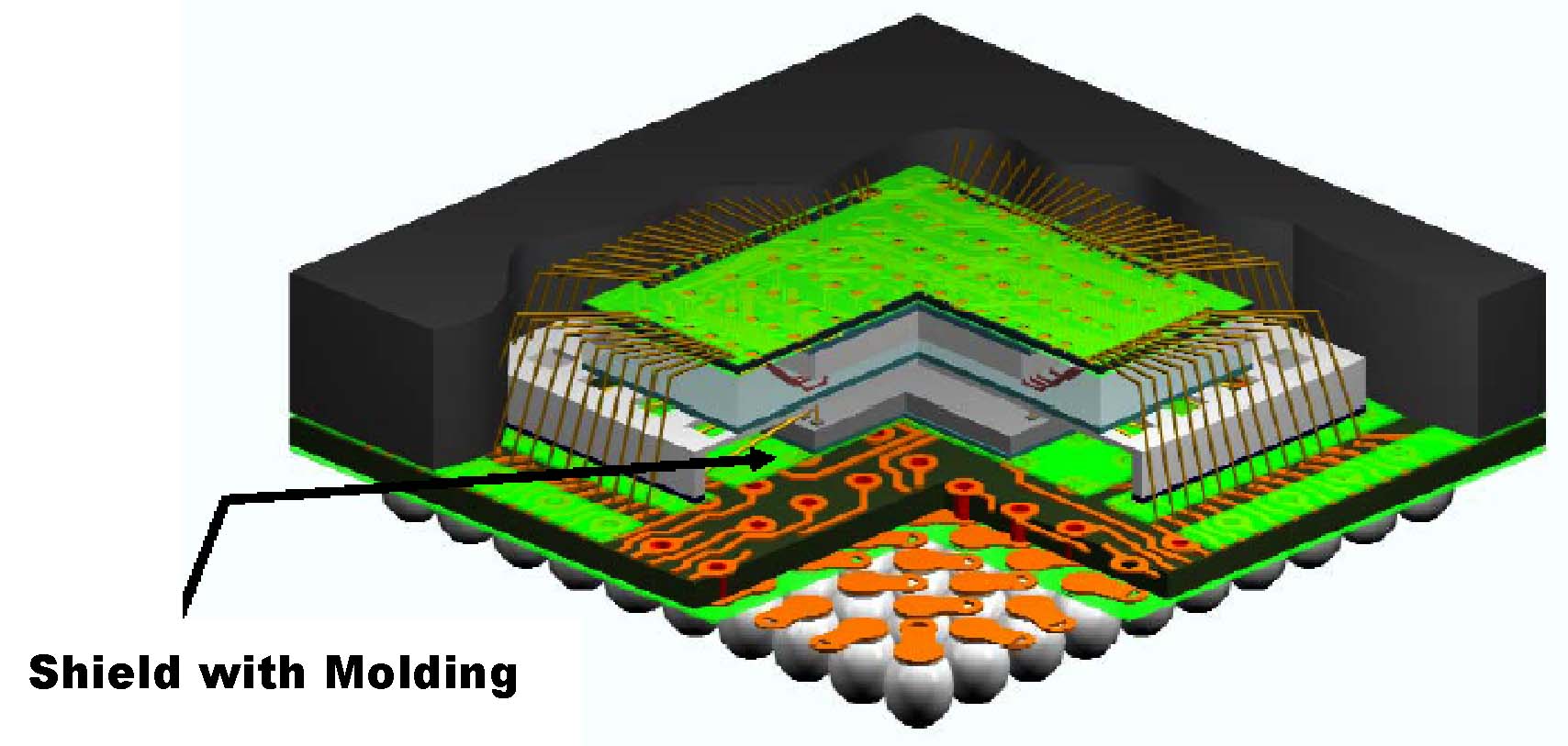

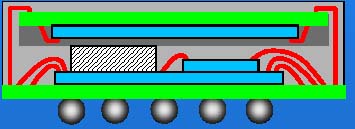

丂PiP偼丄帠慜偵CSP壔偝傟丄僥僗僩偝傟偨僷僢働乕僕傪愊傒廳偹偰昗弨偺儌乕儖僪僷僢働乕僕偲偡傞曽幃偩丅暷STATS ChipPAC幮CTO偺Marcos Karnezos巵偵傛傟偽乽僥僗僩嵪昳傪傾僙儞僽儕偡傞偨傔嵟廔廂棪偼99.7%偵払偡傞乿偲尵偆丅傑偨僷僢働乕僕撪晹偵揹帴僔乕儖僪婡峔傪撪憰偱偒傞偙偲側偳偺棙揰傪帩偪丄摨巵偍傛傃慜弎偺Vardaman巵偼乽摨媄弍偼暷QUALCOMM幮偱擣掕偝傟丄尰嵼JEDEC昗弨壔偺僾儘僙僗偑恑傔傜傟偰偄傞乿偲弎傋偨丅

暷STATS ChipPAC幮偺PiP(Package-in-Package)偺峔憿奣擮恾(僔乕儖僪婡峔偺撪憰)

暷STATS ChipPAC幮偺PiP(Package-in-Package)偺峔憿奣擮恾(抐柺)

| 丒 | 儃僩儉儌僕儏乕儖偼廃埻偵嵟彫1mm偺愙懕僄儕傾偑昁梫丅 |

| 丒 | 僩僢僾儌僕儏乕儖傪昗弨僷僢働乕僕偵偡傞丅(JEDEC昗弨壔) |

| 丒 | 奜宎悺朄偼JEDEC偺儌乕儖僪BGA婯奿偵弨嫆 |

| (尰峴偼慡崅1.4mm僷僢働乕僕偵懳墳丄1.2mm壔傪恑傔偰偄傞丅) |

丂WLP傗SiP娭楢偺曬崘偺拞偱嵟屻偵拲栚傪廤傔偨偺偼撈Infenion Technologies幮偺Georg Meyer-Berg巵偺曬崘偱丄柉惗壙奿懷偺40Gbps僩儔儞僔乕僶儌僕儏乕儖傪栚巜偡偲偄偆摨幮偺僾儘僕僃僋僩X- IGA (Si-Interconnect Grid Array)偑憤妵揑偵徯夘偝傟偨丅

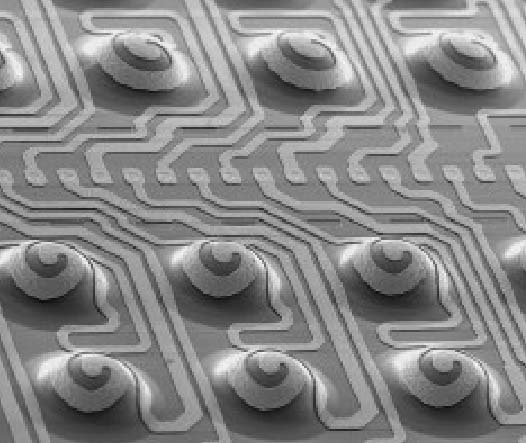

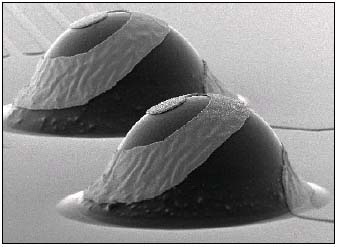

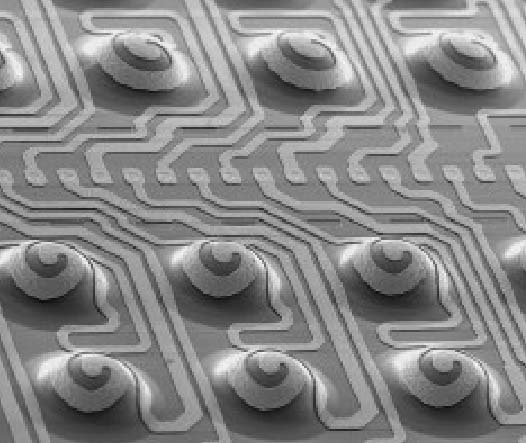

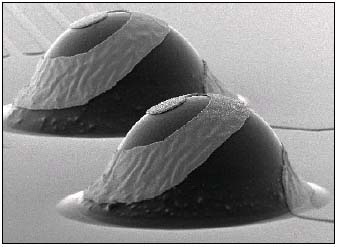

丂X-IGA偼丄婎杮揑偵Si婎斅傪梡偄偨儅儖僠僠僢僾WLP丅僼儕僢僾僠僢僾幚憰偝傟傞儀傾僟僀傪Si婎斅拞墰晹偵攝抲丄僼傽儞傾僂僩嵞攝慄偱儁儕僼僃儔儖側僌儕僢僪傾儗僀傪宍惉偡傞丅嵟傕儐僯乕僋側晹暘偼丄嬥懏儔儞僪傗儃乕儖丄僶儞僾偺戙傢傝偵宍惉偝傟傞乽ELASTEC乿偲屇偽傟傞峔憿偱丄僄儔僗僩儅嵽椏偺撍婲忋偵嬥懏偺僗僷僀儔儖峔憿偑宍惉偝傟偰偄傞丅

丂摨ELASTEC峔憿偼丄摨幮偑撈Siemens帪戙偵峔憐偝傟丄偙偺KGD Workshop偱傕3擭傎偳慜偵堦晹偺敪昞偑偁傝丄崱夞偺曬崘偵偼乽傛偆傗偔偙偙傑偱棃偨偐乿偲偄偆姶偑偁傞丅偦偺撍婲偼僔儕僐乕儞嵽椏傪僗僥儞僔儖報嶞偟偰宍惉丄僗僷僢僞偲儊僢僉偵傛傝Au/Ni/Cu峔惉偱嵞攝慄憌偲摨帪偵僗僷僀儔儖峔憿傪宍惉偡傞丅偛偔昗弨揑側僾儘僙僗傪巊梡偟丄偙傟傪僂僄僴儗儀儖偱峴側偆偙偲偱掅僐僗僩壔傪恾偭偰偄傞丅

撈Infineon幮丂乽ELASTEC(R)乿偵傛傞僌儕僢僪傾儗僀晹暘

撈Infineon幮丂乽ELASTEC(R)乿偺奼戝幨恀

丂摨巵偵傛傞偲乽抏椡惈偺偁傞戝僶儞僾偲僗僷僀儔儖嬥懏偵傛傞峔憿偱丄Si婎斅偺WLP僌儕僢僪傾儗僀偱偁傝側偑傜丄QFP暲傒幚憰怣棅惈傪幚尰偟偨乿偲偄偆丅

丂埲忋丄KGD Packaging and Test Workshop撪梕偺堦晹傪徯夘偟偨丅摨Workshop偺摿挿偺傂偲偮偼丄嶲壛幰偺懡偔偑懾嵼偡傞奐嵜儂僥儖偱孞傝峀偘傜傟傞枅斢抶偔傑偱偺僱僢僩儚乕僉儞僌傗僨傿僗僇僢僔儑儞偲尵偊傛偆丅偦偙偱偼丄僙僢僔儑儞帪娫偱偼暔懌傝側偐偭偨媍榑偑嵞擱偡傞丅僟僀僾儘僟僋僩偵娭傢傞惛塻摍偑廤偆Workshop側傜偱偼偱偁傝丄偙傟偵僫僷偺儚僀儞偑壛惃偡傞丅

崱擭偼擔杮偐傜偺嶲壛幰偑斾妑揑彮側偔丄娭楢偟偨敪昞偼4審偺傒偱偁偭偨丅僟僀僾儘僟僋僩偺庡梫巗応偼丄擔杮傪偼偠傔偲偡傞傾僕傾抧堟偱偁傞丅偦偙偐傜惗傑傟攟傢傟傞傾僀僨傾偲媄弍傪丄2005擭傕傑偨摨帪婜丄摨応強偱奐嵜偝傟傞KGD Packaging and Test Workshop偱徯夘丄傾僺乕儖偟偰偼偄偐偑偩傠偆偐丅

URL 丗http://www.napakgd.com

乽DRI 儗億乕僩乿僔儕乕僘 偺僶僢僋僫儞僶乕偼偙偪傜偱偡

拞搰丂榓岹 (K-NETS 僐儞僒儖僥傿儞僌幮挿)

揹婥捠怣戝妛乮搶嫗搒 挷晍巗乯戝妛堾嵽椏壢妛愱峌 廋巑壽掱 1985擭廋椆

廧桭嬥懏峼嶳姅幃夛幮揹巕嵽椏尋媶強擖幮埲棃丄揹巕丒岝捠怣帠嬈晹栧偵17擭娫嵼愋

1993擭偐傜2001擭傑偱暷崙nCHIP幮丒Flextronics幮偵偰嬈柋廬帠

岝捠怣僨僶僀僗丄敿摫懱僷僢働乕僕儞僌晹嵽丄傾僙儞僽儕丄婎斅幚憰媄弍偺尋媶奐敪丄帠嬈壔丄偍傛傃儅乕働僥傿儞僌妶摦偵廬帠

尰嵼偼撈棫丄媄弍儅乕働僥傿儞僌偍傛傃僐儞僒儖僥傿儞僌偲偟偰暷崙僔儕僐儞僶儗乕偵偰妶摦拞

偙傟傑偱丄戝壨撪婰擮媄弍戝徿丄擔宱嶻嬈怴暦桪廏惢昳徿庴徿

娭楢摿嫋30審埲忋丄妛弍榑暥丒嶨帍婰帠摍幏昅30審埲忋

|  戞11夞丂KGD Packaging & Test Workshop 曬崘

戞11夞丂KGD Packaging & Test Workshop 曬崘