スタックCSPの技術と役割について スタックCSPの技術と役割について

−シリコンバレー MEPTEC主催Die Stacking CSPミーティングより−

中島 和宏 K-NETS コンサルティング社長

2003年1月21日号

正月休みも明けて七草粥の香りも覚めやらぬ一月八日、シリコンバレーにてMEPTEC (Micro-Electronics Packaging & Test Engineering Council)主催によるプライベート・ミーティングが開催された。その席で、以前Amkor社プロダクト・マーケティング・マネージャーで、現在Tessera社ビジネス・デベロップメント・ディレクターのLee Smith氏が講演したスタックCSPに関する報告を中心にまとめてみた。

現在、ネットワーク・サーバーやストレージ・サーバー等を含む高性能コンピュータに利用されるメモリー・モジュール分野、携帯電話やPDA機器等で拡大しているワイヤレス通信分野において高密度化の新しい流れが定着しつつある。それが、半導体チップのスタック(積層)実装技術である。

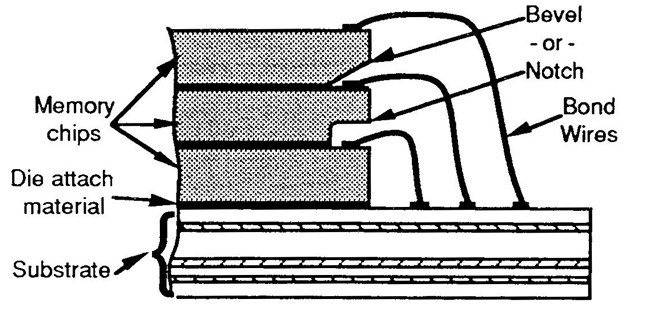

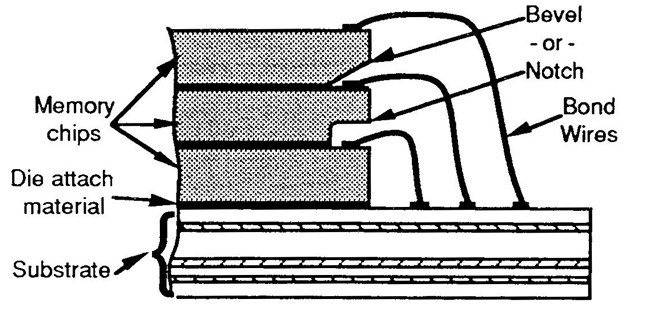

90年代初頭に、マルチ・チップ実装の概念から半導体メモリー・チップのスタック化技術は芽生えた。例えば、米国MMS社やnCHIP社にその足跡が見られる。nCHIP社では、二段目以降に積層される同一サイズの半導体チップの底面両端が、直下段の半導体チップに対するボンディング・ワイヤに接触しないように切削した面取り形状、もしくはノッチ形状にしたスタック技術を1994年に紹介している。(1) また後年、日本の住友金属鉱山によりノッチなしで多段化する改良が加えられた。(2)

面取り、もしくはノッチ付メモリー・スタック実装技術 (1)

近年のハンドヘルド機器の発展、特に携帯電話に対する小型化、薄型化の要求に応えるためFlushメモリーやSRAMのスタック化が見直され、その技術は飛躍的に発達、スタック化されてひとつのパッケージ、例えばスタックCSPとして応用範囲を拡大してきた。 あの小型で薄い筐体の中にデジタルをベースとした機能部分、メモリーを中心とする記憶部分とワイヤレスに必要な高周波やアナログをベースとした機能部分がすべて収まっているのである。 いわゆる小型高密度化技術の集大成といっても良い。

同氏が引用したPortelligent社の調査データによると、ここ三年間で携帯機器の基板(PCB)面積は約26%減少したが、部品サイズは約半分(47%減少)になっている。その結果、単位面積あたりの部品数は約29%増加、また部品あたりのI/O数も増加しているため単位あたりのI/O接続数はなんと約141%も増加したことになる。PDA機器に迫ったデータ管理機能やeMail、インターネット接続、デジタルカメラからムービーまで、携帯電話の性能や機能が著しく向上している現在の状況をみればご納得いただけるであろう。 Intelの調査による情報では、日本において音声通信のみであった初期の携帯電話がしのぎを(まさに)「削った」軽量化競争は、98-99年頃に60gを切ったところでほぼ終焉を迎えた。 それと同時にi-mode携帯電話が出現した。 その頃、機を熟した二段スタックCSPがメモリー・デバイスに採用され、翌年には三段スタックCSPへと発展した。i-modeも新世紀に入って重量60gを切ったところで軽量化競争に加えて先に述べたような性能・機能拡張に移行、さらにFOMAも出現した。 そのような中で2001年末には四段スタックCSPが採用され、最近では半導体メモリー・チップのスタックだけではなく、ベース・バンド用等のロジックICを含めてスタック化する技術に発展している。

- Sharpの嘉田氏およびAmkor当時のLee Smith氏報告より(3) -

一方、高性能コンピュータやサーバーの分野では、TSOPにパッケージ化されたDRAMのスタック実装が一般的となっている。 ところが、このような実装方法では今後のメモリー・モジュール高密度化やメモリー・バス伝送速度の高速化に限界が見えてきているため、携帯機器同様にスタックCSP化されたデバイス実装への転換が図られている。

例えば、メモリーのデータ・レート性能で比較してみると、従来のリードフレームを利用したパッケージであるTSOPは100-133MHzのSDRAMや133-266MHzのDDR-SDRAM等に使用され、恐らくDDR2-SDRAM 400MHzあたりでは限界を超えるであろうと言われている。 一方、CSPタイプのパッケージはすでに500-600MHzのRDRAMや800MHzあるいはそれ以上のDRDRAMに使用可能である。 そもそもロジックICの性能が、一般に言われるムーアの法則に沿って飛躍的に向上しているのに対して、メモリー・デバイスの性能向上はメモリー・モジュールやバス構造も含めてこれに追いついていない。 むしろ、それらの性能ギャップは年々拡大する傾向にある。もちろんこれはメモリー・デバイスのパッケージ構造だけに起因するものではないが、その中でもCSPやさらにスタックCSPといった実装構造・技術の果たす役割は大きい。

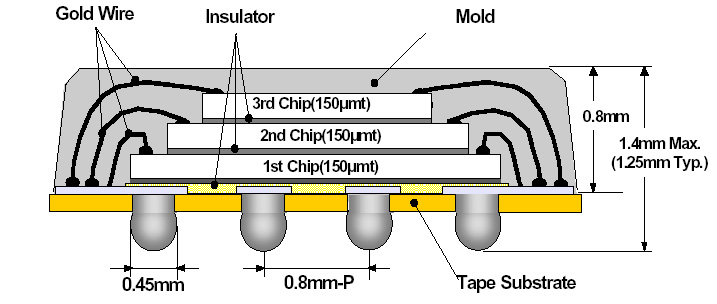

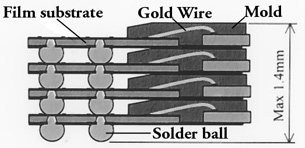

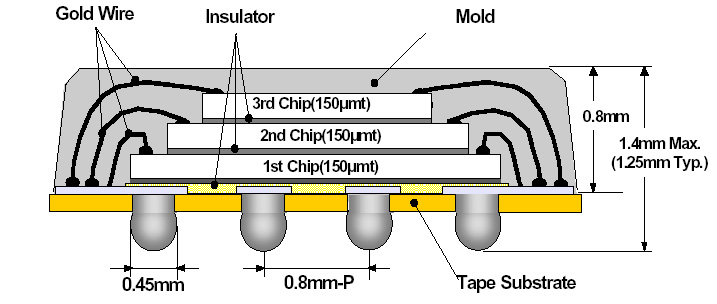

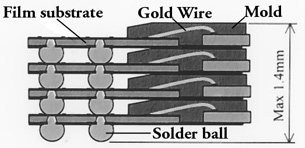

メモリー・モジュールの高密度化という点で、例えば66ピンのTSOPと60ピンのフィルム型CSP(Tessera社のμZTM)を比較した場合、半導体チップのサイズが15x7mmであるのに対してTSOPのパッケージサイズは約22x11mm、CSPでは約15x10mmと小さい。 面積にして約四割の削減である。 このようなフィルム型CSPは、また薄型化とスタック化にも適している。東芝とミスズがスタックを前提として開発したフィルム・スタック型CSP、例えばハーフ・ミリCSPでは、四段スタックによる実装において高さは1.4mm以下に過ぎず、これはおよそTSOPひとつ分の高さ(1.1mm以下)である。(4) これらの技術を用いることにより、メモリー・モジュールにはおよそ八倍のメモリー容量が実装可能となった。

したがって、CSP関連パッケージのDRAM系メモリー・デバイスに対する適用は今後2-3年間で急激に増加すると見られている。 現在DRAMに対するCSPタイプ・パッケージの利用は四半期あたり20-30百万個程度に過ぎないが、2004年度にはおよそ十倍に拡大するとの予測である。これは、現在高性能コンピュータやサーバーの分野においてメモリー・モジュール実装の主流を占めているSDRAM系TSOPが、小型化(特に高さ)・高密度実装化・高性能化(DDR、DDR2等)への要求、そして結果的にはシステム・コストの低減に応えるためにCSP、およびスタックCSP化されていくと考えているためである。

フィルム・スタック型CSP(ハーフ・ミリCSP)四段スタックの断面模式図 (4)

このような状況の中で、スタックCSPのように半導体チップの積層構造を持つ実装形態のパッケージを開発、製品として広く認知されていくためには、技術的な要求事項として以下のような項目に留意する必要がある。

・ 頑丈な構造で確固たる信頼性を、パッケージ単体および基板実装後の両レベルで持たなくてはならない。

・ 短・長期的に見てコスト効果が得られなくてはならない。

・ 異種半導体チップの積層化など集積化が容易に行える構造で、かつ、チップ個数やチップサイズ等の変更に即応可能である。

・ 伝送性能や放熱管理を含めた現行そして将来の特性要求を満たす可能性を持っている。

・ 配線やI/O密度、さらに積載可能チップ個数等の拡張性が考慮されている。

果たしてこれらすべての要求を満たしているのかどうかは別として、Smith氏が所属していたAmkor社が取り揃えているスタック構造のパッケージ群は、一部半導体メーカーのライセンスにより製造しているStacked CSP(S-CSP)やS-PBGA、さらにFlip Chipと組み合わせたFS-CSP、FS-BGA等である。また、Tessera社で開発を進めている新しい構造は、μZTM Fold-Overという名称のフィルム折畳み積層構造タイプと、μZTM Ball-Stackと呼ばれるフィルム積層構造タイプである。いずれも両社のWEBサイト、http://www.amkor.com および http://www.tessera.com で紹介されているのでご参照いただきたい。

参考文献

(1) D. B. Tuckerman, et. al., "Laminated Memory: A New 3-Dimentional Packaging Technology for MCMs," pp.58-63, Proceedings of the 1994 IEEE Multi-Chip Module Conference, MCMC-94

(2) Tadashi Kimura, et. al., "Bare Chip Stacking Technology for High Density Packaging," pp.37-38, Proceedings of the 11th JIPC Annual Meeting, March, 1997

(3) Morihiro Kada (Sharp) and Lee Smith (Amkor), "Advancements in Stacked Chip Scale Packaging (S-CSP)," Proceedings of Pan Pacific Microelectronics Symposium Conf., January, 2000

(4) Kenji Miyajima (Toshiba), Mitsuru Chino (Misuzu), "Stacked Half-Milli CSP," Proceedings of the 26th IEMT Symposium, October, 2000

「DRI レポート」シリーズ のバックナンバーはこちらです

中島 和宏 (K-NETS コンサルティング社長)

電気通信大学(東京都 調布市)大学院材料科学専攻 修士課程 1985年修了

住友金属鉱山株式会社電子材料研究所入社以来、電子・光通信事業部門に17年間在籍

1993年から2001年まで米国nCHIP社・Flextronics社にて業務従事

光通信デバイス、半導体パッケージング部材、アセンブリ、基板実装技術の研究開発、事業化、およびマーケティング活動に従事

現在は独立、技術マーケティングおよびコンサルティングとして米国シリコンバレーにて活動中

これまで、大河内記念技術大賞、日経産業新聞優秀製品賞受賞

関連特許30件以上、学術論文・雑誌記事等執筆30件以上

主な執筆論文(記事)等

* Observation of the bend of garnet thick films in LPE growth; The 47th Autumn Meeting of Japan Society of Applied physics, Sep. 1986

* Optical Isolator using an improved type of (YbTbBi)3Fe5O12 thick film; The 12th Annual Conference on Magnetics in Japan, Oct. 1988

* New design of a Polarization-Independent Optical Isolator with High Performance; The 5th MMM-Intermag Conference, IEEE Transactions on Magnetics, Vol. 27, No. 6, 1991

* Characterization of Thermally and Electrically Conductive Epoxy Adhesive on its Silver Concentration; The 8th International Microelectronics Conference, Apr. 1994

* Thermal Analysis of Plastic Encapsulated Multi-Chip Packages; The Micro-Electronics Packaging & Test Engineering Council Report, Vol. 1, No. 5, 1997

* CSP Primer for Original Equipment Manufacturers - CSP Trends In On-board Productions; Chip Scale Review, Vol. 2, No. 4, Sep. 1998

* Why Use Bare Chip-On-Board Technology? ; Electronic Packaging & Production - The Premier Resource for Electronics Manufacturing, Mar. 1999

* CSP On-Board Assembly: Implementation and Qualification; SMT - The Magazine for Electronics Assembly, Jul. 1999

* A Novel Localizable HDI-PWB Solution; Conference Proceedings of SMTA International, Sep. 2000 and HDI - The Magazine of High-Density Interconnect, Vol. 3, Dec. 2000

* ファイバアレイ: V溝不要で自由にファイバを固定、高い位置精度と信頼性を両立, Electronic Journal 8月号 (2002年)

|

スタックCSPの技術と役割について

スタックCSPの技術と役割について